随着摩尔定律放缓,缩小晶体管之间的空间变得越来越困难,封装技术的创新变得尤为重要。据日媒报道,台积电正与谷歌等美国科技巨头合作,开发新的芯片封装技术。

避开μ-bumps 凸点的封装技术

台积电现当下采用的3D技术名为SoIC,可以垂直与水平地进行芯片封裝,可以将处理器、内存和传感器等几种不同类型的芯片堆叠和连接在一起。这种方法使整个芯片组更小,更强大,更节能。

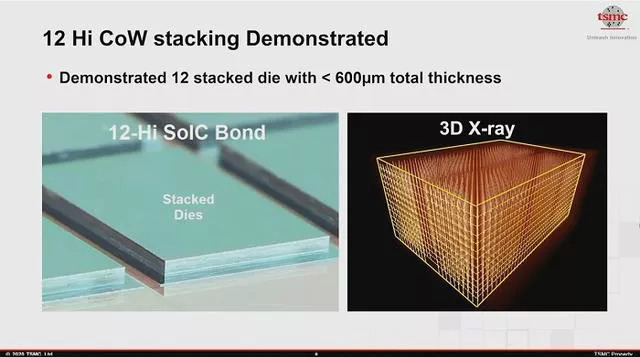

由台积电分享的一张幻灯片可知,这项关键技术的复杂度,远超以往的硅中介层或芯片堆叠工艺。因其允许在不使用任何 μ-bumps 凸点的情况下堆叠硅芯片,而是直接将金属层彼此对准并键合到硅片上。

其设计理念是每层都可具有不同的逻辑元素,比如 IO 或 SRAM 。此外某层也可以是无源的,以充当其它有源层之间的隔热层。如 PPT 所示,这种设计的最大厚度为 600 μm,意味着单层厚度要控制在 50 μm 以下,而传统标准管芯堆叠解决方案上的凸点间距也是 50 μm 左右。

至于 SoIC,N7 / N6 工艺下的混合键合间距为 9 μm,N5 工艺更是可以缩减到 6 μm 。这表明台积电拥有一些令人印象深刻的线性制造和晶圆减薄技术,以实现如此高水平的管芯对准与一致性。

谷歌、AMD将成首批SoIC芯片客户

据日经新闻透露,援引知情人士的话表示,台积电计划在其正在台湾苗栗市兴建的芯片封装厂使用其新型3D堆叠技术。消息人士称,谷歌和AMD将成为其首批SoIC芯片的客户,并将帮助台积电对这些芯片进行测试和认证。该工厂的建设计划明年完工,将于2022年开始大规模生产。

知情人士表示,台积电当然不会试图取代所有传统的芯片封装厂商,但它的目标是服务于那些处于金字塔顶端的高端客户,这样那些财力雄厚的芯片开发商,如苹果、谷歌、AMD和英伟达,就不会把台积电留给竞争对手。

另一位芯片封装行业专家表示:“这些新的芯片堆叠技术需要先进的芯片制造专业知识以及大量的计算机模拟来实现精确的堆叠,因此传统芯片封装供应商很难介入。”

有知情人士表示,谷歌计划将SolC工艺生产的芯片用于自动驾驶系统和其他应用。谷歌在设计自己的芯片方面相对较新,目前在其数据中心服务器中用于人工智能计算。

业内趣谈台积电有动静,中芯国际也会有动静

自从开始发展半导体领域后,台积电就一直是关注的对象,最近有消息称刚从美国回来的台积电副总曹敏正式重返入职。在工艺上,台积电工艺最领先5nm领先,其次三星5nm就是刚能量产,而后面的巨头英特尔,连7nm都成问题。

而中芯国际在短短几年,从28nm制程工艺到14nm制程工艺,相较于在14nm挤牙膏多年的英特尔也能碰一碰。

即使没有相应设备,工艺上也另辟蹊径,推出N+1工艺,现在已经第2代正在产品验证,小量试产,N+2更是不用极紫外光刻机,就能生产高制程芯片,虽然还在完善中,但距离推出不会太久。

据日媒报道透露,中芯国际也在考虑建立类似台积电SolC的先进芯片封装能力,并已向台积电的一些供应商订购设备,以运营一条小规模的先进封装生产线。

台积电拒绝就具体客户置评,但表示,由于计算任务比过去更加多样化,要求也更高,半导体和封装技术有必要共同发展,客户对先进芯片封装服务的需求正在增加。

点击此处关注,获取最新资讯!

我的评论

最新评论

2020-11-26

2020-11-20